# Comparación de inversores multinivel asimétrico para aplicaciones en energías renovables

Christopher Jesús Rodríguez Cortés, Cesar Augusto Limones Pozos, José

Miguel Sosa Zúñiga

Christopherrodriguezcortes@gmail.com (alumno)

Cesar.limones@itesi.edu.mx

Jmsosa@itesi.edu.mx

#### Resumen

En el presente trabajo se comparan cinco inversores multinivel con fuentes asimétricas para aplicaciones de energías renovables. Se describen las diferentes topologías, y además se analiza en cada inversor los estados de los interruptores que permiten generar los diferentes niveles de voltaje. Se presenta una comparativa de acuerdo al número de componentes que conforma cada topología y el número máximo de niveles de voltaje generado por cada inversor.

# Introducción

Los inversores multinivel son convertidores de electrónica de potencia que produce un voltaje de salida con una forma de onda escalonada parecida a una sinusoidal, a partir de una o más fuentes de voltaje de DC, teniendo como ventaja, la reducción del contenido armónico. Recientemente los inversores multinivel han surgido como una alternativa para generación de energía eléctrica por medio de fuentes renovables. Se han utilizado inversores multinivel para inyectar energía eléctrica a partir de la energía generada por los sistemas fotovoltaicos FV y sistemas eólicos.

Los inversores multinivel presentan mayores ventajas a comparación a los inversores que producen dos o tres niveles de voltaje a la salida denominados binivel. Las principales ventajas son, distorsión armónica baja, filtros de salida más pequeños, los inversores multinivel permiten reducir el estrés eléctrico entres sus componentes y también permite trabajar con frecuencias bajas, lo que permite aumentar la eficiencia del sistema [1].

Una alternativa para aumentar el número de niveles en los inversores multinivel es la conexión de inversores en cascada. Los inversores conectados en cascada se pueden clasificar en simétricos y asimétricos. Los inversores simétricos constan de dos o más topologías iguales alimentadas con fuentes de DC separadas, donde el valor de voltaje cada fuente es igual. Para generar un mayor número de niveles a la salida se deben agregar mayor número de inversores conectados en cascada. Sin embargo, la principal desventaja es que al incrementar el número de dispositivos semiconductores la eficiencia disminuye.

Los inversores asimétricos constan de dos o más topologías conectadas en cascada con fuentes de alimentación DC separadas de distintos valores, normalmente en relaciones de 1:2 o 1:3 de esta manera, este tipo de inversores pueden generar un mayor número de niveles de voltaje con un menor uso de dispositivos semiconductores.

En este artículo se presenta una comparativa de cinco diferentes inversores multinivel con fuentes asimétricas las cuales tienen aplicación en sistemas de generación de energía por medio de fuentes renovables. En la sección II se realiza Vol. 6 (2019) 7º Encuentro de Jóvenes Investigadores

la descripción del proyecto. En la sección IV se describe la justificación del proyecto realizado. En la sección V se describe la metodología de la investigación, donde se plantea las diferentes topologías de inversor multinivel con fuentes asimétricas. En la sección VI se realiza una comparativa entre las diferentes topologías reportadas en la literatura. Finalmente, en la sección VII se describen las conclusiones del trabajo.

# Objetivo

Estudiar las topologías de inversores multinivel asimétricos reportados en la literatura, para aplicaciones de sistemas de generación de energía eléctrica por medio de fuentes renovables.

# Justificación

Debido a los problemas del medio ambiente que son causados por la generación de energía eléctrica por uso de combustibles fósiles, se está recurriendo a la generación de energía eléctrica mediante el uso de energías renovables como son los sistemas FV. La generación de energía eléctrica usando sistemas fotovoltaicos ha surgido como una nueva alternativa, debido a su confiabilidad, fácil instalación y la posibilidad que de que la instalación pueda estar cerca de los usuarios [2]. Para realizar la inyección de energía eléctrica generada por los sistemas fotovoltaicos, se debe adecuar su forma de onda de salida de corriente directa, a una forma de corriente alterna. Para realizar la adecuación de energía de CD a CA se utiliza los convertidores de electrónica de potencia CD-CA llamados inversores [2].

Los inversores se pueden clasificar, con respecto a los niveles de voltaje de salida que pueden generar como binivel o multinivel. Estos últimos tienen mayores ventajas con respecto a los binivel, como son, la reducción de contenido armónico. Para que los inversores multinivel generen mayor número de niveles de voltaje a la salida se deben conectar mayor cantidad de interruptores al convertidor de

electrónica de potencia, teniendo como consecuencia la disminución de la eficiencia.

La contribución de este trabajo es el estudio de diferentes inversores multinivel asimétricos reportados en la literatura, ya que estos pueden generar mayor número de niveles de voltaje a la salida con menor uso de interruptores de potencia teniendo la ventaja, del incremento de los niveles de eficiencias en los sistemas de electrónica de potencia.

# Metodología

En esta sección se presenta cinco topologías de inversores multinivel con fuentes asimétricas los cuales son aplicados en sistemas de generación de energía eléctrica por medio de fuentes renovables. Donde se describe la topología de acuerdo al número de componentes que los conforman y se describe la estrategia de modulación implementada en las diferentes topologías para producir los diferentes niveles de voltaje.

# Inversor multinivel asimétrico 9L-TT-HB

En la Fig. 1 se muestra el inversor multinivel propuesto en [3], para aplicaciones de energías renovables. La topología está conformada por la conexión en cascada de un inversor Tipo-T y puente completo. El inversor Tipo-T se conforma de cuatro transistores bipolar de compuerta aislada. Donde dos de ellos estas dispuestos como una rama y los otros dos son parte de un interruptor bidireccional. Este inversor produce tres niveles de voltaje a la salida, el máximo voltaje producido por el inversor es  $\frac{V_{CD}}{2}$ , debido al voltaje  $V_{CD}$ , es dividido en dos por la conexión en paralelo de los capacitores. El inversor puente completo se conforma de cuatro interruptores unidireccional, donde produce un máximo de tres niveles de voltaje de salida con una amplitud máxima en del bus de CD.

El inversor mostrado en la Fig. 1 nombrado 9L-TT-HB por sus iniciales en inglés (9 Level-Type-T- H-Bridge), tiene fuentes de CD de valores de voltajes asimétricos para genera mayor número de niveles. El inversor 9L-TT-HB tiene tres capacitores y ocho dispositivos semiconductores. La relación que existe entre las fuentes de CD es de 1: 1.15 generando un máximo de nueve niveles de voltaje de salida.

La estrategia de modulación propuesta en [3], para generar la secuencia de activación de los interruptores para el inversor 9L-TT-HB, está basada en la estrategia SPWM con desplazamiento en niveles descritas en [8]-[9], la cual genera la secuencia de pulsos por medio de la comparación de una señal de referencia senoidal y seis señales triangulares denominadas portadoras.

**Tabla I.** Estados para el inversor 9L-TT-HB.

| Niveles | $T_1$ | <i>T</i> <sub>2</sub> | $\overline{T}_1$ | $\overline{T}_2$ | $T_3$ | $\overline{T}_3$ | $T_4$ | $\overline{T}_4$ | $v_{out}$           |

|---------|-------|-----------------------|------------------|------------------|-------|------------------|-------|------------------|---------------------|

| 1       | 1     | 0                     | 0                | 1                | 1     | 0                | 0     | 1                | $2V_{CD}$           |

| 2       | 0     | 0                     | 1                | 1                | 1     | 0                | 0     | 1                | $1.5V_{CD}$         |

| 3       | 0     | 1                     | 1                | 0                | 1     | 0                | 0     | 1                | $V_{CD}$            |

| 4       | 1     | 0                     | 0                | 1                | 1     | 0                | 1     | 0                | $0.5V_{\rm CD}$     |

| 5       | 0     | 0                     | 1                | 1                | 1     | 0                | 1     | 0                | $0V_{CD}$           |

| 6       | 0     | 1                     | 1                | 0                | 1     | 0                | 1     | 0                | -0.5V <sub>CD</sub> |

| 7       | 1     | 0                     | 0                | 1                | 0     | 1                | 1     | 0                | -V <sub>CD</sub>    |

| 8       | 0     | 0                     | 1                | 1                | 0     | 1                | 1     | 0                | -1.5V <sub>CD</sub> |

| 9       | 0     | 1                     | 1                | 0                | 0     | 1                | 1     | 0                | -2V <sub>CD</sub>   |

Fig. 1. Inversor hibrido 9L-TT-HB con voltaies asimétrico

En la Tabla I se muestran los estados de los interruptores para el inversor 9L-TT-HB para generar los diferentes voltajes de salida  $V_{out}$ . Se observa que el voltaje máximo obtenido es dos veces el voltaje  $V_{CD}$ .

#### Inversor multinivel asimétrico de 63 de 63 niveles

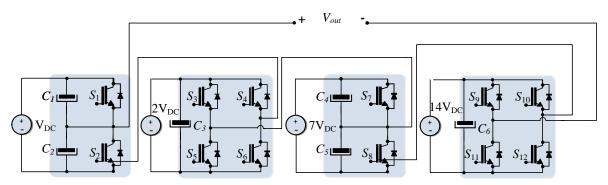

El inversor multinivel asimétrico propuesto en [4] para aplicaciones en sistemas fotovoltaicos, está conformado por cuatro inversores conectados en cascada. Donde dos de ellos son inversores medio puente y los otros dos son inversores puente completo. Donde los inversores tienen fuentes de DC de valores de voltaje asimétricos teniendo una relación entre las fuentes de CD de 1: 2; 7; 14, como se muestra en la Fig. 2 generando un máximo de 63 niveles de voltaje de salida.

Fig. 2. Inversor multinivel asimétrico 63-niveles.

La técnica de modulación propuesta [4] para el inversor 63 niveles, está basada en la modulación vector espacial. La modulación se obtiene por el estado de conmutación del inversor descrita en [11].

#### Inversor multinivel asimétrico 13L

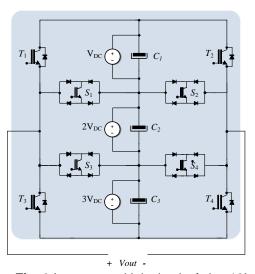

En la Fig. 3 se muestra un inversor multinivel asimétrico propuesto en [5] generando un máximo de 13 niveles para aplicaciones de sistemas FV conectados a la red, nombrado 13L por sus siglas en inglés (13-Level). El inversor multinivel está conformado por cuatro interruptores unidireccional (T1, T2, T3 y T4) y cuatro interruptores bidireccionales como S1, S2, S3 y S4 para la generación de 13 niveles de voltaje a la salida. Para que el inversor genere 13 niveles de voltaje a la salida debe existir una relación en las fuentes de voltaje CC de 1: 2: 3.

Tabla II. Estados para el inversor 13L.

| Niveles | T | $T_2$ | <i>T</i> <sub>3</sub> | $T_4$ | <b>S</b> <sub>1</sub> | $S_2$ | $S_3$ | $S_4$ | $v_{out}$         |

|---------|---|-------|-----------------------|-------|-----------------------|-------|-------|-------|-------------------|

| 1       | 1 | 0     | 0                     | 1     | 0                     | 0     | 0     | 0     | 6V <sub>CD</sub>  |

| 2       | 1 | 0     | 0                     | 0     | 0                     | 0     | 0     | 1     | 5V <sub>CD</sub>  |

| 3       | 0 | 0     | 0                     | 1     | 1                     | 0     | 0     | 0     | $4V_{CD}$         |

| 4       | 0 | 0     | 0                     | 0     | 1                     | 0     | 0     | 1     | 3 V <sub>CD</sub> |

| 5       | 1 | 0     | 0                     | 0     | 0                     | 1     | 0     | 0     | $2V_{CD}$         |

| 6       | 0 | 0     | 0                     | 1     | 0                     | 0     | 1     | 0     | $V_{CD}$          |

| 7       | 0 | 0     | 1                     | 1     | 0                     | 0     | 0     | 0     | 0V                |

| 8       | 0 | 0     | 1                     | 0     | 0                     | 0     | 0     | 1     | - V <sub>CD</sub> |

| 9       | 0 | 1     | 0                     | 0     | 1                     | 0     | 0     | 0     | $-2V_{CD}$        |

| 10      | 0 | 0     | 0                     | 0     | 0                     | 1     | 1     | 0     | $-3V_{CD}$        |

| 11      | 0 | 0     | 1                     | 0     | 0                     | 1     | 0     | 0     | $-4V_{\rm CD}$    |

| 12      | 0 | 1     | 0                     | 0     | 0                     | 0     | 1     | 0     | -5V <sub>CD</sub> |

| 13      | 0 | 1     | 1                     | 0     | 0                     | 0     | 0     | 0     | -6V <sub>CD</sub> |

Fig. 3 Inversor multinivel asimétrico 13L. Vol. 6 (2019) 7º Encuentro de Jóvenes Investigadores

En la Tabla II, se muestran los estados de los interruptores para el inversor 13L. Se observa que se genera los trece niveles de voltaje a la salida mediante la suma de los voltajes de cada fuente.

La técnica de modulación propuesta en [5], para generar la secuencia de activación de los interruptores está basada en la técnica SPWM la cual genera la secuencia de activación por medio de la comparación de una señal de referencia senoidal y seis portadoras desplazadas en niveles.

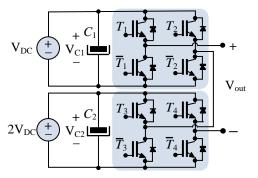

# Inversor multinivel asimétrico 7L-CHB

El inversor multinivel puente completo en cascada de siete niveles, nombrado 7L-CHB por sus siglas en inglés (7 Level Cascaded H-Bridge), se muestra en la Fig. 4. El inversor 7L-CHB está conformado por la conexión en cascada de dos inversores de puente completo y la relación que existe entre las fuentes de alimentación es de 1: 2 lo que permite un máximo de siete niveles de voltaje de salida. El inversor 7L-CHB tiene dos capacitores y ocho dispositivos semiconductores. En la Tabla III se muestran los estados para generar los diferentes voltajes de salida  $V_{13}$  se observa que el voltaje máximo es tres veces el valor de  $V_{DC}$ .

**Fig 4.** Inversor 7L-CHB con voltajes asimétricos.

**Tabla III.** Estados para el inversor 7L-CHB.

| Niveles | $T_1$ | <i>T</i> <sub>2</sub> | $\overline{T}_{I}$ | $\overline{T}_2$ | $T_3$ | $\overline{T}_3$ | $T_4$ | $\overline{T}_4$ | $v_{13}$          |

|---------|-------|-----------------------|--------------------|------------------|-------|------------------|-------|------------------|-------------------|

| 1       | 1     | 0                     | 0                  | 1                | 1     | 0                | 0     | 1                | $3V_{CD}$         |

| 2       | 1     | 1                     | 0                  | 0                | 1     | 0                | 0     | 1                | $2V_{CD}$         |

| 3       | 1     | 0                     | 0                  | 1                | 1     | 0                | 1     | 0                | $V_{CD}$          |

| 4       | 1     | 1                     | 0                  | 0                | 1     | 0                | 1     | 0                | $0V_{CD}$         |

| 5       | 0     | 1                     | 1                  | 0                | 1     | 0                | 1     | 0                | -V <sub>CD</sub>  |

| 6       | 1     | 1                     | 0                  | 0                | 0     | 1                | 1     | 0                | $-2V_{\rm CD}$    |

| 7       | 1     | 0                     | 0                  | 1                | 1     | 0                | 0     | 1                | -3V <sub>CD</sub> |

La técnica de modulación propuesta en [3], para el inversor 7L-CHB, está basada en la técnica SPWM la cual genera la secuencia de conmutación de los

interruptores por medio de la comparación de una señal de referencia y 6 portadoras desplazadas en niveles.

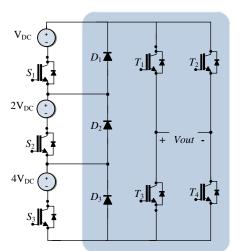

# Inversor multinivel de unidad básica asimétrica 15L-HB

En la Fig. 5 se muestra un inversor multinivel asimétrico propuesto en [6], donde es nombrado 15L-HB por sus siglas en inglés (15-Level-H-Bridge). La estructura propuesta consiste en una unidad básica asimétrica y un puente completo. El inversor está compuesto por siete dispositivos semiconductores y tres diodos. En la Tabla IV se muestran los estados para generar los diferentes voltajes de salida  $V_{out}$ . Se observa que el voltaje máximo es de  $7V_{CD}$  cuando se tiene una relación entre las fuentes de 1:2:4, para generar un máximo de 15 niveles de voltaje.

Fig 5. Inversor multinivel de unidad básica asimétrica 15L-HB.

**Tabla IV.** Estados para el inversor multinivel de unidad básica asimétrica.

| Niveles | $S_1$ | $S_2$ | $S_3$ | <i>T</i> <sub>1</sub> | <i>T</i> <sub>2</sub> | <i>T</i> <sub>3</sub> | $T_4$ | v <sub>out</sub>  |

|---------|-------|-------|-------|-----------------------|-----------------------|-----------------------|-------|-------------------|

| 1       | 1     | 1     | 1     | 1                     | 0                     | 0                     | 1     | $7V_{CD}$         |

| 2       | 0     | 1     | 1     | 1                     | 0                     | 0                     | 1     | 6V <sub>CD</sub>  |

| 3       | 1     | 0     | 1     | 1                     | 0                     | 0                     | 1     | 5V <sub>CD</sub>  |

| :       | ÷     | ÷     | :     | :                     | :                     | :                     | ÷     | :                 |

| 7       | 1     | 0     | 0     | 1                     | 0                     | 0                     | 1     | V <sub>CD</sub>   |

| 8       | 0     | 0     | 0     | 1                     | 0                     | 1                     | 0     | 0                 |

| 9       | 1     | 0     | 0     | 0                     | 1                     | 1                     | 0     | - V <sub>CD</sub> |

| :       | ÷     | ÷     | :     | :                     | ÷                     | ÷                     | ÷     | :                 |

| 13      | 1     | 0     | 1     | 0                     | 1                     | 1                     | 0     | $-5V_{CD}$        |

| 14      | 0     | 1     | 1     | 0                     | 1                     | 1                     | 0     | -6V <sub>CD</sub> |

| 15      | 1     | 1     | 1     | 0                     | 1                     | 1                     | 0     | -7V <sub>CD</sub> |

#### Resultados

En esta sección se muestra una comparativa entre las topologías de acuerdo al número de componentes que conforma cada topología y el número máximo de niveles de voltaje generado por cada inversor. Donde se realizó la comparativa basándose en las características principales como lo son;

- I. Número de dispositivos semiconductores. En los sistemas PV el costo inicial de los inversores se ve afectado directamente por los números de dispositivos semiconductores utilizados. Por lo tanto, es importante reducir el costo del inversor, utilizando un número menor número de dispositivos semiconductores. Además, la eficiencia se ve afectada por las pérdidas de potencia en los dispositivos semiconductores. Por lo tanto, es más conveniente implementar topologías con menor uso de dispositivos semiconductores.

- II. Número de niveles de voltaje. Un requerimiento para realizar la interconexión de los sistemas FV con la red eléctrica tienen que cumplir estándares internacionales como la IEEE-519 [12]. Donde establece el nivel máximo permitido de contenido armónico para la inyección de potencia activa a la red eléctrica. Una alternativa para reducir el contenido armónico es aumentar los niveles de voltaje. Por lo tanto, los inversores multinivel con fuentes asimétricas presentan menor contenido armónico a diferencias de los inversores con fuentes simétricas, debido que generan mayor número de niveles de voltaje con menor uso de dispositivos semiconductores.

III. Tabla V. Comparación de los inversores multinivel.

| Inversor               | 9L-TT-HB | 63L      | 13L   | 7L-CHB | 15L-HB |  |

|------------------------|----------|----------|-------|--------|--------|--|

| Interruptores          | 8        | 12       | 8     | 8      | 7      |  |

| Capacitores            | 3        | 3        | 3     | 2      | 0      |  |

| Diodos                 | 0        | 0        | 16    | 0      | 3      |  |

| Relación de voltaje DC | 1:1.5    | 1;2;7;14 | 1:2:3 | 1:2    | 1:2:4  |  |

| Max. Niveles generados | 9        | 63       | 13    | 7      | 15     |  |

En la Tabla V se resume las características de los inversores multinivel. El inversor multinivel 63 niveles tiene mayor número de semiconductores a comparación de las demás topologías teniendo como consecuencia que el prototipo sea de mayor tamaño y que el costo se incremente. Pero tiene la ventaja que genera mayor número de niveles de voltaje a la salida haciendo que la forma de salida se asemeje más a una forma sinudoidal y que tamaño de filtro de acoplamiento sea menor.

El inversor 7L-CHB es el que genera un menor número de niveles de voltaje a la salida teniendo mayor contenido armónico a comparación de las demás topologías.

El inversor 15L-HB es que utiliza menor dispositivos semiconductores a comparación de las demás topologías, generando un máximo de 15 niveles teniendo como ventaja menor contenido armónico en el voltaje de salida, requiriendo un valor de menor en el filtro de acoplamiento a comparación de topología 9L-TT-HB y 7L-CHB.

#### Conclusión

En el presente trabajo se realizó el estudio de las diferentes topologías de inversores multinivel reportadas en la literatura para aplicaciones en energías renovables. Una de la ventajas de los inversores multinivel asimétricos, es la generación de mayor número de niveles de voltaje con menor uso de dispositivos semiconductores y la disminución del contenido armónico a comparación a los inversores binivel. Como se observó de las diferentes topologías de inversores el que presento mayores ventajas es el inversor 15L-HB, debido que utiliza menor número de dispositivos semiconductores a comparación de las demás topologías reportadas.

### Referencias

- [1] J. Venkataramanaiah, Y. Suresh, A. K. Panda, "A review on symmetric, asymmetric, hybrid and single DC sources based multilevel inverter topologies," *Renewable and Sustainable Energy Reviews*, Volume 76, 2017, Pages 788-812, ISSN 1364-0321, doi: 10.1016/j.rser.2017.03.066.

- [2] G. Váquez, P. P. Martinez-Rodriguez, J.M.Sosa. "Comparative Analyisi of Single-Phase Grid Connected Transformerless Photovoltaic Inverter Topologies" IEEE International Autumn Meeting on Power Electronics and Computing (ROPEC), (2013).

- [3] Christopher J. Cortés, Cesar A. Limones-Pozos, J.M. Sosa Zuñiga, "Analisis de eficiencia y THD de un inversor multinivel TT/HB de 9 niveles para ER" Congreso Internacional de Energía UG (CIENERGÍA), (2019).

- [4] Sumit K. Chattopadhyay, "New Asymmetric Multilevel Inverter Topology Suitable for Solar PV Applications with Varying Irradiance" DOI 10.1109/TSTE.2017.2692257.

- [5] Madan Kumar Das, Kartick Chandra Jana, "Performance evaluation of an asymmetrical reduced switched multi-level inverter for grid-connected PV system", The Institution of Engineering and Techonology, doi: 10.1049/ietrpg.2016.0895.

- [6] Rasoul Shalchi Alishah, Daryoosh Nazarpour, "New Hybrid structure for multilevel inverter with fewer numer of components for high-voltage levels", IET Power Electronics, ISSN 1755-4535, doi: 10.1049/iet-pel.2013.0156

- [7] P. Jana, S. Chattopadhyay, S. Maiti, P. Bajpai and C. Chakraborty, "Hybrid modulation technique for binary asymmetrical cascaded multilevel inverter for PV application," 2016 IEEE International Conference on Power Electronics, Drives and Energy Systems (PEDES), Trivandrum, 2016, pp. 1-6. doi: 10.1109/PEDES.2016.7914265.

- [8] J.Chavarria, D. Biel, F. Guinjoan, C. Meza, and J.J. Negroni, "Energy balance control of pv cascaded multilevel grid-connected inverter under level-shifeted and phase-shifted pwms", IEEE trans. On Industrial Electronics, Vol. 60(1), pp.98-111, January 2013.

- [9] J.A. Juárez-Abad, J.Linares-Flores and M. A. Contreras-Ordaz, "FPGA-based level-shift PWM for an asymmetric multilevel trinary inverter", 2016 13<sup>th</sup> International Conference on Power Electronics (CIEP), Guanajuato, Mexico, 2016, pp. 161-165.0

- [10] Ferrero Delgado Julio, (2018) "Filtro para la frecuencia de conmutación de un inversor fotovoltaico". Tesis de grado en Ingenieria Eléctrica. Universidad de Vallladolid, Valladolid.

- [11] H. W. Van der Broeck, H.-C. Skudelny "Analisis and realization of a pulsewidth modulator based on voltajes spaces vectors" IEEE Transactions on Industry Applications, Vol. 24, No. 1, enero/febrero, 1988, Pags. 142-150.

- [12] IEEE Std 519 2014, IEEE Recommended Practice and Requirements for Harmonic Control in Electrics Power Systems, USA.